👋 Hello, friends! Dr. Molina here 👨🔧

Welcome to Dr.Molina Newsletter, where I break down Magnetic design for you every week, in

4 minutesthe time needed.

One of my favorite hobbies after APEC is reviewing interesting articles or presentations. This week, I bring you a tip from the seminar of Juan Rivas from Stanford University. I’m not an expert in GaN or SiC, so learning small tips is helpful.

The story [1] of Prof. Juan Rivas started with a mismatched loss estimation in his MHz range power converters. He studied a little more in detail and found the guilty parameter: the parasitic capacitance Coss.

After this discovery, he analyzed the impact of this parameter in GaN and SiC, ending with a direct comparison between both devices.

The Final Battle: SiC Vs. GaN

The first battle is about losses due to Coss in the function of the Frequency.

GaN device losses increase while SiC keeps constant.

Point for SiC.

However, if we check the losses at high frequencies, we find that Gate Driving losses at SiC are huge compared to GaN due to the SiC high capacitance in the gate, Qg.

Point for GaN.

There is a solution for SiC driving problems. Using a resonant driver, which reduces 5x the losses.

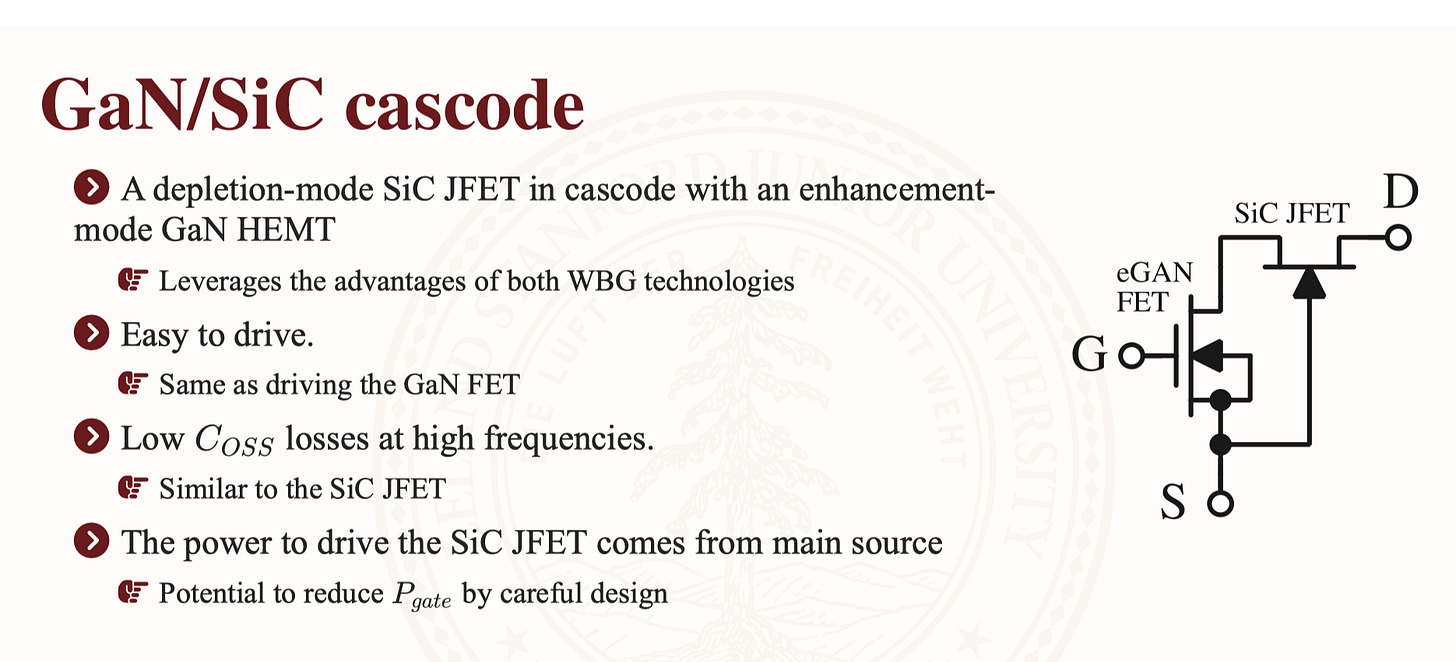

However, Prof. Rivas suggested combining the best SiC and GaN in a Cascode device with low Coss and low Qg.

Another chapter of the battle between GaN and SiC took place in this presentation, with a hybrid solution as a winner. I’ll continue exploring what the industry thinks about GaN and SiC.

What do you think about it?

I hope you have found this edition interesting 🤓.

Reference

[1] Switching Losses Associated with Output-Capacitance Hysteresis, JM Rivas, APEC 2023

If you missed….some of the most widely read articles in the Dr.Molina Magnetics Newsletter: